Work: ssingh@groq.com

Personal: satnam@raintown.org

Personal: satnam6502@gmail.com

Professional: s.singh@acm.org

Professional: s.singh@ieee.org

Bio: https://satnam.fpcastle.com/bio

Talks: https://satnam.fpcastle.com/talks

satnam6502

satnam6502

satnam6502

satnam6502

satnam6502

satnam6502

Google Scholar

Google Scholar

ORCID-ID: 0000-0002-2017-4310

ORCID-ID: 0000-0002-2017-4310

Researchr Profile

Personal website: raintown.org

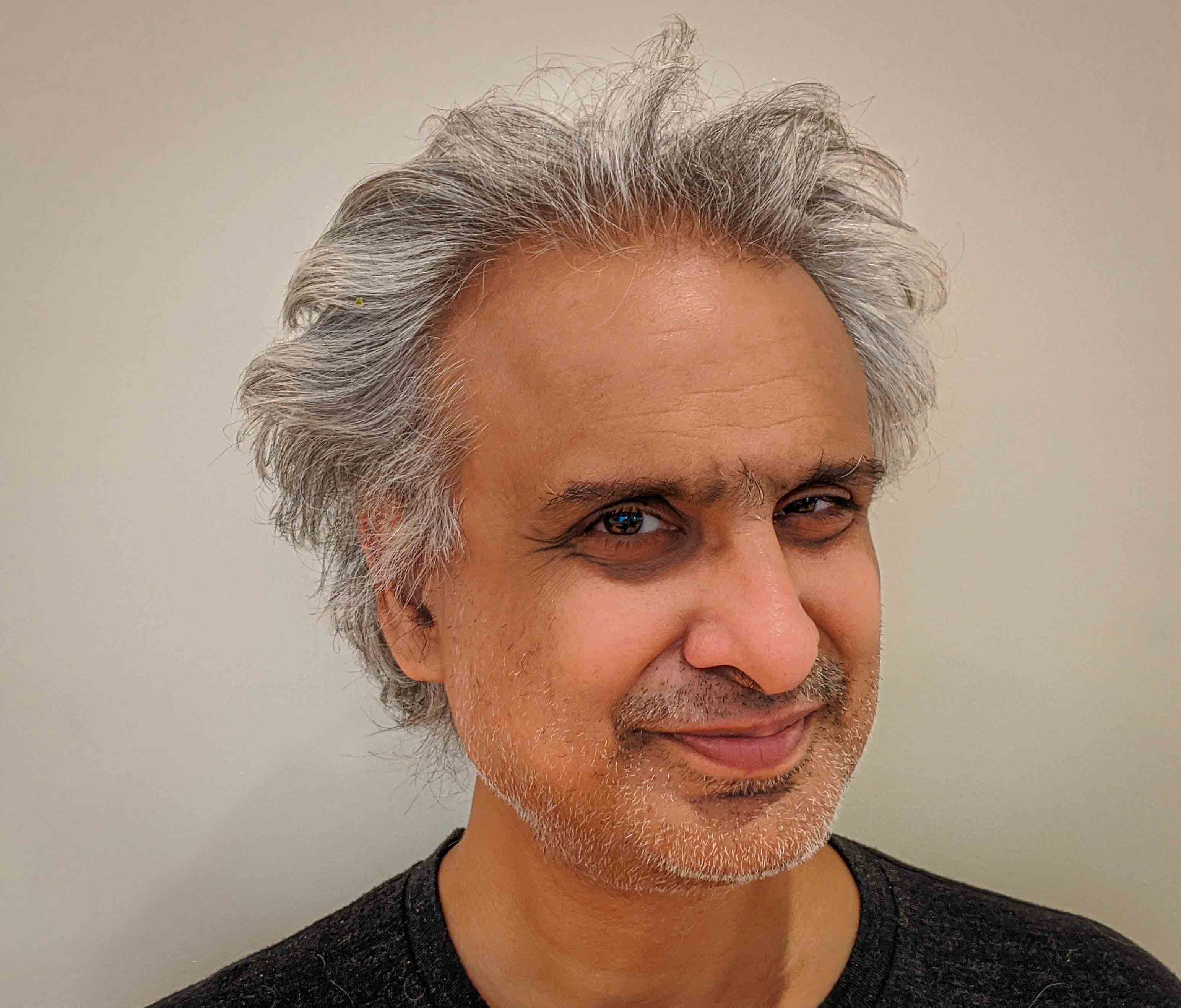

Satnam Singh

I’m a computer scientist and hardware engineer working for the AI chip company Groq in California that deploys LLMs (large language models) at scale with very low latency. There I have been working on the design of hardware for the power management of machine learning inference chips, the formal verification of machine learning hardware, and the front-end components of a compiler for machine learning models (MLIR, ONNX, JAX, PyTorch, Tensorflow, StableHLO).

My background is in topics like functional programming; formal methods; hardware design esp. FPGAs and machine learning ASICs; and distributed systems orchestration. I was an early member of the Kubernetes team at Google.

I previously worked at Google (machine learning chips, cluster management), Facebook (Android optimization), Microsoft (parallel and concurrent programming) and Xilinx (Lava DSL for hardware design, formal verification of hardware). I started my career as an academic at the University of Glasgow (FPGA-based application acceleration and functional programming, software-defined radio).

My research interests include functional programming in Haskell, high level techniques for hardware design (Lava, Bluespec, DSLs in Haskell, Coq and C#), formal methods (SAT-solvers, model checkers, theorem provers), formally verified hardware/software co-design, FPGAs, and concurrent and parallel programming.

I am a Senior Member of the ACM and IEEE and a Fellow of the IET. I am also an elected member of IFIP WG2.8 (functional programming) and IFIP WG2.11 (program generation). I previously served as an elected member of ACM SIGPLAN. I have held part-time or honorary positions at The University of Birmingham, Imperial College London, the University of Washington, and the University of Santa Cruz (UCSC). I am currently a visiting academic at the Department of Computer Science and Technology at the University of Cambridge.

If you need a bio for a talk you can find some at http://satnam.fpcastle.com/bio.

Employment

| Employer | Role and Location |

|---|---|

| 2021 — present | Fellow, Groq Mountain View, California |

| 2019 — 2021 | Software Engineer, Google Research (formerly Google AI) Mountain View, California, USA Also Lecturer at UC Santa Cruz, Jack Baskin School of Engineering |

| 2017 — 2019 | Software Engineer, Google X Mountain View, California, USA |

| 2015 — 2017 | Software Engineer, Facebook Menlo Park, California, USA |

| 2012 — 2015 | Software Engineer, Google Mountain View, California, USA |

| 2006 — 2011 | Researcher, Microsoft Research Cambridge, UK Also Professor of Reconfigurable Systems University of Birmingham Visiting Lecturer Imperial College, London |

| 2004 — 2006 | Principal Architect, Microsoft Redmond, Washington, USA Also Affiliate faculty at EE University of Washington (2005) |

| 1998 — 2004 | Principal Engineer, Xilinx San Jose, California, USA |

| 1991 - 1997 | Lecturer (Assistant Professor) Dept. Electrical Engineering Department, then Computing Science Department University of Glasgow, UK Also Consultant, Requirements Reuse British Telecom London and Ipswich, UK (1992 - 1993) Software Engineer (GUI development and Hardware Synthesis) Compass Design Automation / VLSI Technology Sophia Antipolis, France (1992) |

| 1987 - 1987 | Programmer (Unix, C) European Silicon Structures Bracknell, UK |

| 1986 - 1986 | Programmer (MS-DOS, Turbo Pascal) Glasgow Dental Hospital, Glasgow, UK |

Education

| When | What |

|---|---|

| 1983 — 1987 | BSc (Hons) Computing Science University of Glasgow, UK |

| 1987 — 1990 | PhD Computing Science University of Glasgow, UK |